lpgbtfpga_decoder Entity Reference

lpgbtfpga_decoder - Uplink FEC decoder More...

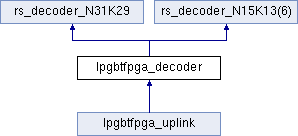

Inheritance diagram for lpgbtfpga_decoder:

Detailed Description

lpgbtfpga_decoder - Uplink FEC decoder

Decodes the received data and corrects error WHEN possible. The decoding is based on the N=31, K=29 and SymbWidth=5 or the N=15, K=13 and SymbWidth=4 implementation of the Reed-Solomon scheme depending on the configuration (FEC5 or FEC12).

Definition at line 19 of file lpgbtfpga_decoder.vhd.

The documentation for this class was generated from the following file:

- /mnt/lpgbt-fpga-sources/uplink/lpgbtfpga_decoder.vhd

Entities | |

| behavioral | architecture |

| lpgbtfpga_decoder - Uplink FEC decoder More... | |

Libraries | |

| ieee | |

| Include the IEEE VHDL standard LIBRARY. | |

Use Clauses | |

| ieee.std_logic_1164.all | |

| work.lpgbtfpga_package.all | |

| Include the lpGBT-FPGA specific package. | |

Generics | |

| DATARATE | integer range 0 to 2 |

| Datarate selection can be: DATARATE_10G24 or DATARATE_5G12. | |

| FEC | integer range 0 to 2 |

| FEC selection can be: FEC5 or FEC12. | |

Ports | |

| uplinkClk_i | in std_logic |

| uplinkClkOutEn_i | in std_logic |

| fec5_data_i | in std_logic_vector ( 233 downto 0 ) |

| Data input from de-interleaver for FEC5 decoding (redundant on upper/lower part of the bus @5.12Gbps) | |

| fec5_fec_i | in std_logic_vector ( 19 downto 0 ) |

| FEC input from de-interleaver for FEC5 decoding (redundant on upper/lower part of the bus @5.12Gbps) | |

| fec12_data_i | in std_logic_vector ( 205 downto 0 ) |

| Data input from de-interleaver for FEC12 decoding (redundant on upper/lower part of the bus @5.12Gbps) | |

| fec12_fec_i | in std_logic_vector ( 47 downto 0 ) |

| FEC input from de-interleaver for FEC12 decoding (redundant on upper/lower part of the bus @5.12Gbps) | |

| fec5_data_o | out std_logic_vector ( 233 downto 0 ) |

| Data output for FEC5 decoding (redundant on upper/lower part of the bus @5.12Gbps) | |

| fec12_data_o | out std_logic_vector ( 205 downto 0 ) |

| Data output for FEC12 decoding (redundant on upper/lower part of the bus @5.12Gbps) | |

| fec5_correction_pattern_o | out std_logic_vector ( 233 downto 0 ) |

| fec12_correction_pattern_o | out std_logic_vector ( 205 downto 0 ) |

| bypass | in std_logic |

| Bypass uplink FEC (test purpose only) | |

1.8.5

1.8.5