lpgbtfpga_uplink Entity Reference

lpgbtfpga_uplink - Uplink wrapper (top level) More...

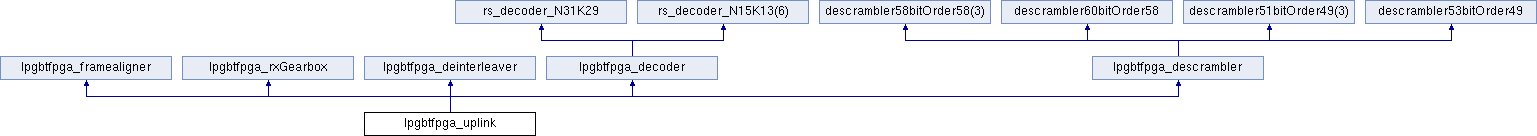

Inheritance diagram for lpgbtfpga_uplink:

Detailed Description

lpgbtfpga_uplink - Uplink wrapper (top level)

The lpgbtfpga_uplink wrapper implements the logic required for the frame alignement, the frame construction and the decoding/descrambling of the data.

Definition at line 20 of file lpgbtfpga_uplink.vhd.

The documentation for this class was generated from the following file:

- /mnt/lpgbt-fpga-sources/lpgbtfpga_uplink.vhd

Entities | |

| behavioral | architecture |

| lpgbtfpga_uplink - Uplink wrapper (top level) More... | |

Libraries | |

| ieee | |

| Include the IEEE VHDL standard LIBRARY. | |

Use Clauses | |

| ieee.std_logic_1164.all | |

| work.lpgbtfpga_package.all | |

| Include the lpGBT-FPGA specific package. | |

Generics | |

| DATARATE | integer range 0 to 2 |

| Datarate selection can be: DATARATE_10G24 or DATARATE_5G12. | |

| FEC | integer range 0 to 2 |

| FEC selection can be: FEC5 or FEC12. | |

| c_multicyleDelay | integer range 0 to 7 := 3 |

| Multicycle delay: Used to relax the timing constraints. | |

| c_clockRatio | integer |

| Clock ratio is mgt_Userclk / 40 (shall be an integer) | |

| c_mgtWordWidth | integer |

| Bus size of the input word (typically 32 bits) | |

| c_allowedFalseHeader | integer |

| Number of false header allowed (among c_allowedFalseHeaderOverN) to avoid unlock on frame error. | |

| c_allowedFalseHeaderOverN | integer |

| Number of header checked to know wether the lock is lost or not. | |

| c_requiredTrueHeader | integer |

| Number of consecutive correct header required to go in locked state. | |

| c_bitslip_mindly | integer := 1 |

| Number of clock cycle required when asserting the bitslip signal. | |

| c_bitslip_waitdly | integer := 40 |

| Number of clock cycle required before being back in a stable state. | |

Ports | |

| uplinkClk_i | in std_logic |

| Uplink datapath clock (Transceiver Rx User clock, typically 320MHz) | |

| uplinkClkOutEn_o | out std_logic |

| Clock enable indicating a new data is valid. | |

| uplinkRst_n_i | in std_logic |

| Uplink reset signal (Rx ready from the transceiver) | |

| mgt_word_i | in std_logic_vector ( ( c_mgtWordWidth - 1 ) downto 0 ) |

| Input frame coming from the MGT. | |

| userData_o | out std_logic_vector ( 229 downto 0 ) |

| --! User output (decoded data). The payload size varies depending on the | |

| EcData_o | out std_logic_vector ( 1 downto 0 ) |

| EC field value received from the LpGBT. | |

| IcData_o | out std_logic_vector ( 1 downto 0 ) |

| IC field value received from the LpGBT. | |

| bypassInterleaver_i | in std_logic |

| Bypass uplink interleaver (test purpose only) | |

| bypassFECEncoder_i | in std_logic |

| Bypass uplink FEC (test purpose only) | |

| bypassScrambler_i | in std_logic |

| Bypass uplink scrambler (test purpose only) | |

| mgt_bitslipCtrl_o | out std_logic |

| Control the Bitslip/RxSlide port of the Mgt. | |

| dataCorrected_o | out std_logic_vector ( 229 downto 0 ) |

| Flag allowing to know which bit(s) were toggled by the FEC. | |

| IcCorrected_o | out std_logic_vector ( 1 downto 0 ) |

| Flag allowing to know which bit(s) of the IC field were toggled by the FEC. | |

| EcCorrected_o | out std_logic_vector ( 1 downto 0 ) |

| Flag allowing to know which bit(s) of the EC field were toggled by the FEC. | |

| rdy_o | out std_logic |

| Ready SIGNAL from the uplink decoder. | |

| frameAlignerEven_o | out std_logic |

| Number of bit slip is even (required only for advanced applications) | |

Member Data Documentation

|

Port |

EC field value received from the LpGBT.

datarate/FEC configuration:

- FEC5 / 5.12 Gbps: 112bit

- FEC12 / 5.12 Gbps: 98bit

- FEC5 / 10.24 Gbps: 230bit

- FEC12 / 10.24 Gbps: 202bit

Definition at line 52 of file lpgbtfpga_uplink.vhd.

1.8.5

1.8.5